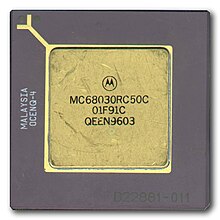

The Motorola 68030 ("sixty-eight-oh-thirty") is a 32-bit microprocessor in the Motorola 68000 family. It was released in 1987. The 68030 was the successor to the Motorola 68020, and was followed by the Motorola 68040. In keeping with general Motorola naming, this CPU is often referred to as the 030 (pronounced oh-three-oh or oh-thirty).

| |

| General information | |

|---|---|

| Launched | 1987 |

| Designed by | Motorola |

| Performance | |

| Max. CPU clock rate | 16 MHz to 50 MHz |

| Data width | 32 bits |

| Address width | 32 bits |

| Cache | |

| L1 cache | 256 bytes each for instruction and data, 16 lines of 4 entries of 4 bytes each, direct mapped[1][2] |

| Architecture and classification | |

| Instruction set | Motorola 68000 series |

| Physical specifications | |

| Transistors |

|

| Package | |

| Products, models, variants | |

| Variant |

|

| History | |

| Predecessor | Motorola 68020 |

| Successor | Motorola 68040 |

The 68030 is essentially a 68020 with a memory management unit (MMU) and instruction and data caches of 256 bytes each. It added a burst mode for the caches, where four longwords can be loaded into the cache in a single operation. The MMU was mostly compatible with the external 68851 that would be used with the 68020,[3] but being internal allowed it to access memory one cycle faster than a 68020/68851 combo. The 68030 did not include a built-in floating-point unit (FPU), and was generally used with the 68881 and the faster 68882. The addition of the FPU was a major design note of the subsequent 68040. The 68030 lacks some of the 68020's instructions, but it increases performance by ≈5% while reducing power draw by ≈25%.

The 68030 features 273,000 transistors. A lower-cost version was also released, the Motorola 68EC030, lacking the on-chip MMU. It was commonly available in both 132-pin QFP and 128-pin PGA packages. The poorer thermal characteristics of the QFP package limited that variant to 33 MHz; the PGA 68030s included 40 MHz and 50 MHz versions. There was also a small supply of QFP packaged EC variants.

The 68030 can be used with the 68020 bus, in which case its performance is similar to 68020 that it was derived from. However, the 68030 provides an additional synchronous bus interface which, if used, accelerates memory accesses up to 33% compared to an equally clocked 68020. The finer manufacturing process allowed Motorola to scale the full-version processor to 50 MHz. The EC variety topped out at 40 MHz.

Usage

editThe 68030 was used in many models of the Apple Macintosh II and Commodore Amiga series of personal computers, NeXT Cube, later Alpha Microsystems multiuser systems, and some descendants of the Atari ST line such as the Atari TT and the Atari Falcon. It was also used in Unix workstations such as the Sun Microsystems Sun-3x line of desktop workstations (the earlier "sun3" used a 68020), Apollo Computer's DN3500 and DN4500 workstations,[4] laser printers and the Nortel Networks DMS-100 telephone central office switch. More recently[when?], the 68030 core has also been adapted by Freescale into a microcontroller for embedded applications.

LeCroy has used the 68EC030 in certain models of their 9300 Series digital oscilloscopes including “C” suffix models[5]: 87-88 and high performance 9300 Series models,[5] along with the Mega Waveform Processing hardware option for 68020-based 9300 Series models.[5]

Variants

editThe 68EC030 is a low cost version of the 68030, the difference between the two being that the 68EC030 omits the on-chip memory management unit (MMU) and is thus essentially an upgraded 68020.

The 68EC030 was used as the CPU for the low-cost model of the Amiga 4000, and on a number of CPU accelerator cards for the Commodore Amiga line of computers. It was also used in the Cisco Systems 2500 Series router, a small-to-medium enterprise computer internetworking appliance. Additionally it was also used as the primary processor in a number of Alpha Microsystems Eagle mini-computers.

The 50 MHz speed is exclusive to the ceramic PGA package, the plastic '030 stopped at 40 MHz.

Technical data

edit| CPU clock rate | 16, 20, 25, 33, 40, 50 MHz, except for MC68EC030 available in 25 and 40 MHz | [1] |

| Internal split-cache modified Harvard architecture | [1] | |

| Address bus | 32 bit | [6] |

| Data bus | 32 bit | [6] |

| Cache | 256 bytes each for instruction and data, 16 lines of 4 entries of 4 bytes each, direct mapped | [1][2] |

| dynamic bus sizing | [1] | |

| burst memory interface | [1] | |

| Performance | 18 MIPS @ 50 MHz | [1] |

See also

editReferences

edit- ^ a b c d e f g "MC68030 Product Summary Page". Freescale. 2012. Archived from the original on October 6, 2014.

- ^ a b "MC68030 User Manual" (PDF). Motorola. 1990.

- ^ Gord, Roy (May 2, 1990). "68851 PMMU and 68030 MMU". Archived from the original on March 3, 2023. Retrieved May 24, 2017.

Neither the PMMU nor the 68030 MMU constitutes a proper superset of the other. The PMMU has instructions and registers not found in the 68030 MMU, while the latter has registers not on the PMMU. However, in a typical Unix implementation little work would needed [sic] to port PMMU specific code to the 68030.

- ^ Tim Hunkler (July 1996). "Survival Guide for Apollo Workstations". Retrieved October 13, 2022.

- ^ a b c LeCroy 1996 Test & Measurement Product Catalog, 9300 Series Hardware Options, Mega Waveform Processing, Pages 66-67

- ^ a b "Motorola 68030 (MC68030) microprocessor family". cpu-world.com. November 17, 2012.

External links

edit- 68030 images and descriptions at cpu-collection.de

- Official information about the Freescale MC68030 microcontroller

- Motorola 68k family data sheets at bitsavers.org

- Extraordinarily rare, pictures, (Shared) of the 68030 emulator pre-silicon breadboard. ( before they layout the silicon, they made a simulator out of discrete logic )